# MAR ATHANASIUS COLLEGE OF ENGINEERING (Government Aided & Autonomous)

Kothamangalam 686 666

# Affiliated to APJ Abdul Kalam Technological University Thiruvananthapuram

# Master of Technology (M. Tech) Curriculum - 2024

# **COLLEGE VISION AND MISSION**

#### VISION

Excellence in education through resource integration.

#### MISSION

The institution is committed to transform itself into a centre of excellence in Technical Education upholding the motto "Knowledge is Power."

This is to be achieved by imparting quality education to mould technically competent

professionals with moral integrity, ethical values and social commitment, and by promoting

innovative activities in the thrust areas emerging from time to time

# MAR ATHANASIUS COLLEGE OF ENGINEERING

# (GOVT. AIDED & AUTONOMOUS)

# **M.TECH CURRICULUM AND SCHEME-2024**

#### **Department of Electronics and Communication Engineering**

#### (VLSI and Embedded Systems)

#### **PROGRAM OUTCOMES – PO**

Outcomes are the attributes that are to be demonstrated by a graduate after completing the programme

- **PO1:** An ability to independently carry out research/investigation and development work in engineering and allied streams

- **PO2:** An ability to communicate effectively, write and present technical reports on complex engineering activities by interacting with the engineering fraternity and with society at large.

- **PO3:** An ability to demonstrate a degree of mastery over the area as per the specialization of the program. The mastery should be at a level higher than the requirements in the appropriate bachelor program

- **PO4:** An ability to apply stream knowledge to design or develop solutions for realworld problems by following the standards

- **PO5:** An ability to identify, select and apply appropriate techniques, resources and stateof-the-art tool to model, analyse and solve practical engineeringproblems.

- **PO6:** An ability to engage in life-long learning for the design and development of the stream related problems taking into consideration sustainability, societal, ethical and environmental aspects. Also to develop cognitive skills for project management and finance which focus on Industry and Entrepreneurship.

The departments conducting the M.Tech programme shall define their own PSOs, if required, and evaluation shall also be done for the same.

# **SEMESTER I**

| Slot | Course Code | Course                                  | Ma  | arks | L-T-P-S | Hours | Credit |

|------|-------------|-----------------------------------------|-----|------|---------|-------|--------|

| 5101 | Course Coue | Course                                  | CIE | ESE  |         | nours | cicuit |

| A    | M24EC1T101  | Digital CMOS VLSI Design                | 40  | 60   | 4-0-0-4 | 4     | 4      |

| В    | M24EC1T102  | FPGA-Based System Design                | 40  | 60   | 4-0-0-4 | 4     | 4      |

| С    | M24EC1T103  | Design with Advanced<br>Microcontroller | 40  | 60   | 4-0-0-4 | 4     | 4      |

| D    | M24EC1E104A | Programme Elective1                     | 40  | 60   | 3-0-0-3 | 3     | 3      |

| E    | M24EC1E105A | Programme Elective2                     | 40  | 60   | 3-0-0-3 | 3     | 3      |

| J    | M24EC1R106  | Research Methodology & IPR              | 40  | 60   | 2-0-0-2 | 2     | 2      |

| G    | M24EC1L107  | HDL Lab                                 | 60  | 40   | 0-0-3-3 | 3     | 2      |

|      | Total       |                                         | 300 | 400  |         | 23    | 22     |

**Teaching Assistance: 7 hours**

Self-study- 23 Hrs

# **Programme Elective 1**

| Slat | Course Code | Course                                | Marks |     |         |       |        |

|------|-------------|---------------------------------------|-------|-----|---------|-------|--------|

| Slot | Course Coue | Course                                | CIE   | ESE | L-T-P-S | Hours | Credit |

| D    | M24EC1E104A | Physical Design<br>Automation         | 40    | 60  | 3-0-0-3 | 3     | 3      |

| D    | M24EC1E104B | EDA tools                             | 40    | 60  | 3-0-0-3 | 3     | 3      |

| D    | M24EC1E104C | DSP Algorithms and<br>Architecture    | 40    | 60  | 3-0-0-3 | 3     | 3      |

| D    | M24EC1E104D | Advanced Digital Signal<br>Processing | 40    | 60  | 3-0-0-3 | 3     | 3      |

| D    | M24EC1E104E | Electronic Packaging                  | 40    | 60  | 3-0-0-3 | 3     | 3      |

| Slat | Course Code | Course                                           | Marks |     |         |       |        |

|------|-------------|--------------------------------------------------|-------|-----|---------|-------|--------|

| Slot | Course Code | Course                                           | CIE   | ESE | L-T-P-S | Hours | Credit |

| E    | M24EC1E105A | Advanced Digital<br>System Design                | 40    | 60  | 3-0-0-3 | 3     | 3      |

| E    | M24EC1E105B | Digital Design<br>Principles and<br>Applications | 40    | 60  | 3-0-0-3 | 3     | 3      |

| E    | M24EC1E105C | Functional verification<br>with system Verilog   | 40    | 60  | 3-0-0-3 | 3     | 3      |

| E    | M24EC1E105D | ASIC design                                      | 40    | 60  | 3-0-0-3 | 3     | 3      |

| E    | M24EC1E105E | Embedded Operating<br>system                     | 40    | 60  | 3-0-0-3 | 3     | 3      |

# **Programme Elective 2**

# SEMESTER – II

| Slot | Course Code | Course                          | Ma  | irks |         |       |        |

|------|-------------|---------------------------------|-----|------|---------|-------|--------|

| Slot | Course Coue | Course                          | CIE | ESE  | L-T-P-S | Hours | Credit |

| Α    | M24EC1T201  | Analog VLSI Design              | 40  | 60   | 4-0-0-4 | 4     | 4      |

| В    | M24EC1T202  | Sensor Technologies and<br>MEMS | 40  | 60   | 4-0-0-4 | 4     | 4      |

| С    | M24EC1E203A | Programme Elective 3            | 40  | 60   | 3-0-0-3 | 3     | 3      |

| D    | M24EC1E204A | Programme Elective 4            | 40  | 60   | 3-0-0-3 | 3     | 3      |

| E    | M24EC18205  | Industry Integrated<br>Course   | 40  | 60   | 3-0-0-3 | 3     | 3      |

| G    | M24EC1P206  | Mini Project                    | 60  | 40   | 0-0-3-3 | 3     | 2      |

**Teaching Assistance: 7 hours**

| Н | M24EC1L207 | Advanced<br>Microcontroller Lab | 60  | 40  | 0-0-3-3 | 3  | 2  |

|---|------------|---------------------------------|-----|-----|---------|----|----|

|   | Total      |                                 | 320 | 380 |         | 23 | 21 |

# Self-study- 23 Hrs

# **Programme Elective 3**

| Slot | Course Code | Course                    | Marks |     |         |       |        |

|------|-------------|---------------------------|-------|-----|---------|-------|--------|

| 5101 | Course Code | Course                    | CIE   | ESE | L-T-P-S | Hours | Credit |

| С    | M24EC1E203A | Embedded Networking       | 40    | 60  | 3-0-0-3 | 3     | 3      |

| С    | M24EC1E203B | SOC Design                | 40    | 60  | 3-0-0-3 | 3     | 3      |

| С    | M24EC1E203C | VLSI structure for DSP    | 40    | 60  | 3-0-0-3 | 3     | 3      |

| С    | M24EC1E203D | Semiconductor<br>Memories | 40    | 60  | 3-0-0-3 | 3     | 3      |

| С    | M24EC1E203E | Embedded System<br>Design | 40    | 60  | 3-0-0-3 | 3     | 3      |

# **Programme Elective 4**

| SI-4 |             | Comme                        | Ma  | arks |         |       |        |

|------|-------------|------------------------------|-----|------|---------|-------|--------|

| Slot | Course Code | Course                       | CIE | ESE  | L-T-P-S | Hours | Credit |

| D    | M24EC1E204A | Low Power VLSI               | 40  | 60   | 3-0-0-3 | 3     | 3      |

| D    | M24EC1E204B | VLSI System Testing          | 40  | 60   | 3-0-0-3 | 3     | 3      |

| D    | M24EC1E204C | High Speed Digital<br>Design | 40  | 60   | 3-0-0-3 | 3     | 3      |

| D    | M24EC1E204D | Deep Learning                | 40  | 60   | 3-0-0-3 | 3     | 3      |

| D    | M24EC1E204E | Static Timing Analysis       | 40  | 60   | 3-0-0-3 | 3     | 3      |

# **SEMESTER - III**

|      |             | TRACK 1              |                              |       |               |       |        |

|------|-------------|----------------------|------------------------------|-------|---------------|-------|--------|

|      |             |                      | Μ                            | Marks |               |       |        |

| Slot | Course Code | Course               | Course CIE ESE P-S           |       | L-T-<br>P-S   | Hours | Credit |

| A    | M24EC1M301  | *MOOC                | To be completed successfully |       |               |       | 2      |

| В    | M24EC1E302A | Programme Elective5  | 40                           | 60    | 3-0-0-3       | 3     | 3      |

| K    | M24EC1I303  | **Internship         | 50                           | 50    |               | -     | 3      |

| Р    | M24EC1P304  | Dissertation Phase 1 | 100                          |       | 0-0-16-<br>16 | 16    | 11     |

|      | 1           | otal                 | 190                          | 110   |               | 19    | 19     |

|   | TRACK 1I   |                                        |                                 |    |  |    |    |  |  |  |  |

|---|------------|----------------------------------------|---------------------------------|----|--|----|----|--|--|--|--|

| A | M24EC1M305 | * MOOC 1                               | To be completed<br>successfully |    |  | 2  |    |  |  |  |  |

| В | M24EC1M306 | * MOOC 2                               | To be completed succ            | -  |  | 2  |    |  |  |  |  |

| K | M24EC1I307 | ## Internship                          | 50                              | 50 |  |    | 4  |  |  |  |  |

| Р | M24EC1P308 | <sup>###</sup> Dissertation<br>Phase 1 | 100                             |    |  |    | 11 |  |  |  |  |

|   |            | 150                                    | 50                              |    |  | 19 |    |  |  |  |  |

# **Programme Elective 5**

|      |                    |                                                | Marks |     |         |       |        |

|------|--------------------|------------------------------------------------|-------|-----|---------|-------|--------|

| Slot | <b>Course Code</b> | Course                                         | CIE   | ESE | L-T-P-S | Hours | Credit |

| В    | M24EC1E302A        | Embedded Systems for<br>Automotive Application | 40    | 60  | 3-0-0-3 | 3     | 3      |

| В    | M24EC1E302B        | Embedded Systems for<br>Robotics               | 40    | 60  | 3-0-0-3 | 3     | 3      |

| В    | M24EC1E302C        | Machine Learning for<br>Embedded Applications  | 40    | 60  | 3-0-0-3 | 3     | 3      |

| В    | M24EC1E302D        | IoT Based Embedded<br>Systems                  | 40    | 60  | 3-0-0-3 | 3     | 3      |

| В    | M24EC1E302E        | Embedded Systems in<br>Smart Grid              | 40    | 60  | 3-0-0-3 | 3     | 3      |

**Teaching Assistance: 7 hours**

7

Mar Athanasius College of Engineering (Govt. Aided & Autonomous) M Tech Regulations, Curriculum 2024

\*MOOC Course of minimum 8 weeks duration to be successfully completed before the end of fourth semester (starting from semester 1). \*\*Internship- mandatory internship of 6 to 8 weeks ## Internship - mandatory internship of more than 16 weeks

###Dissertation Phase 1 – Should be done in Industry

# TRACK 1 / TRACK 2

In second year, the students can choose either of the two tracks: TRACK 1 or TRACK 2. Track 1 is conventional M.Tech programme in which the dissertation Phase 1 is conducted in college. Track 2 is M.Tech programme designed for students who undergone long term internship (not less than 16 weeks) in industry. An aspirant in track 2 needs to do the dissertation in the industry. The candidates should also be good with performing in-depth research and colluding the conclusions of research led by them. Such students are expected to have the following skills: Technical Skills, Research Skills, Communication Skills, Critical Thinking Skills, and Problem-Solving Skills.

# The eligibility for Track 2:

- Shall have qualified in the GATE or have a SGPA above 8.0 during the first semester, and

- Qualify an interview during the end of second semester by an expert committee constituted by the College.

|                                     |             | TRAC                         | K 1   |     |           |       |        |

|-------------------------------------|-------------|------------------------------|-------|-----|-----------|-------|--------|

| Slot                                | Course Code | Course                       | Marks |     | LTDO      |       | Credit |

|                                     |             |                              | CIE   | ESE | L-T-P-S   | Hours |        |

| Р                                   | M24EC1P401  | <b>Dissertation Phase II</b> | 100   | 100 | 0-0-27-24 | 27    | 18     |

|                                     | Total       | 100 100                      |       |     |           | 27    | 18     |

|                                     |             | TRACI                        | K 1I  |     |           |       |        |

| Р                                   | M24EC1P402  | ##Dissertation Phase II      | 100   | 100 |           |       | 18     |

|                                     | Total       |                              | 100   | 100 |           |       | 18     |

| Total credits in all four semesters |             |                              |       |     |           |       |        |

# **SEMESTER – IV**

<sup>#</sup>Dissertation Phase II- Should be done in Industry

# **COURSE NUMBERING SCHEME**

The course number consists of digits/alphabets. The pattern to be followed is

The course number consists of digits/alphabets. The pattern to be followed is

For General Courses- MYYBBXCSNNFor Elective Courses - MYYBBXCSNNA

- M: MASTERS

- YY: Last two digits of year of regulation

- BB: DEPARTMENT

| Sl. No | Department                     | CoursePrefix |

|--------|--------------------------------|--------------|

| 01     | Civil Engg                     | CE           |

| 02     | Computer Science               | CS           |

| 03     | Electrical & Electronics       | EE           |

| 04     | Electronics & Communication    | EC           |

| 05     | Mechanical Engg                | ME           |

| 06     | Any                            | GE           |

| 07     | External (Industry/N PTEL etc) | EX           |

- X :Specialization number

- S : Semester of Study

- 2- Semesters 1

- 3- Semester 2

- 4- Semester 3

- 5- Semester 4

- C: Course Type

- T- Core Course

- E- Elective Course

- R- Research Methodology & IPRL- Laboratory Course

- S- Industry Integrated CourseI- Internship

- M- MOOC

- P- Project/Dissertation

- NN: Course sequence number

- A: Elective sequence number A/B/C/D/E It is illustrated below: Examples:

M24CE1T202 is a second core course of first specialization offered by the CivilDepartment

#### in semester 2

M24EC1R106 is Research Methodology & IPR offered in semester 1 M24EC1E104A is the first subject of Elective 1 of first specialization offered by the EC Department in semester 1

#### **EVALUATION PATTERN**

#### (i) CORE COURSES

Evaluation shall only be based on application, analysis or design based questions (for both internal and end semester examinations).

#### **Continuous Internal Evaluation: 40 marks**

| Micro project/Course based project   | : | 10 marks |

|--------------------------------------|---|----------|

| Course based task/Seminar/Quiz       | : | 10 marks |

| Test paper 1 (Module 1 and Module 2) | : | 10 marks |

| Test paper 2 (Module 3 and Module 4) | : | 10 marks |

The project shall be done individually (Preferable).

#### End Semester Examination : 60marks

The end semester the college will conduct examination. There will be two parts; Part A and Part B. Part A contain 5 numerical questions (such questions shall be useful in the testing of knowledge, skills, comprehension, application, analysis, synthesis, evaluation and understanding of the students), with 1 question from each module, having 4 marks for each question. Students shall answer all questions. Part B contains 7 questions (such questions shall be useful in the testing of overall achievement and maturity of the students in a course, through long answer questions relating to theoretical/practical knowledge, derivations, problem solving and quantitative evaluation), with minimum one question from each module of which student shall answer any five. Each question can carry 8 marks. Total duration of the examination will be 3 Hrs.

# (ii) ELECTIVE COURSES

Evaluation shall only be based on application, analysis or design based questions (for both internal and end semester examinations).

#### **Continuous Internal Evaluation: 40 marks**

Mar Athanasius College of Engineering (Govt. Aided & Autonomous) M Tech Regulations, Curriculum 2024

| Seminar*                                 | : 10 marks |

|------------------------------------------|------------|

| Course based task/Micro Project//Data    |            |

| Collection and interpretation/Case study | : 10 marks |

| Test paper 1 (Module 1 and Module 2)     | : 10 marks |

| Test paper 2 (Module 3 and Module 4)     | : 10 marks |

\*Seminar should be conducted in addition to the theory hours. Topics for the seminar should be from recent technologies in the respective course.

#### **End Semester Examination: 60 marks**

The end semester the College will conduct examination. There will be two parts; Part A and Part B. Part A will contain 5 numerical/short answer questions with 1 question from each module, having 4 marks for each question (such questions shall be useful in the testing of knowledge, skills, comprehension, application, analysis, synthesis, evaluation and understanding of the students). Students should answer all questions. Part B will contain 7 questions (such questions shall be useful in the testing of overall achievement and maturity of the students in a course, through long answer questions relating to theoretical/practical knowledge, derivations, problem solving and quantitative evaluation), with minimum one question from each module of which student should answer any five. Each question can carry 8 marks. Total duration of the examination will be 3 Hrs.

#### (iii) RESEARCH METHODOLOGY & IPR

#### **Continuous Internal Evaluation: 40 marks**

Preparing a review article based on peer reviewed Original publications in the relevant

| discipline (minimum 10 Publications shall be referred) | : 10 marks |

|--------------------------------------------------------|------------|

| Course based task/Seminar/Quiz                         | : 10 marks |

| Test paper 1 (Module 1 and Module 2)                   | : 10 marks |

| Test paper 2 (Module 3 and Module 4)                   | : 10 marks |

| End Semester Examination                               | : 60 marks |

The end semester examination should be conducted by the college. The time duration will be for 3 Hrs and will contain 7 questions, with minimum one question from each module of which student should answer any five. Each question can carry 12 marks.

#### (iv) INTERNSHIP

Internships are educational and career development opportunities, providing practical experience in a field or discipline. They are structured, short-term, supervised placements often focused around particular tasks or projects with defined timescales. An internship may be compensated or non-compensated by the organization providing the internship. The internship has to be meaningful and mutually beneficial to the intern and the organization. It is important that the objectives and the activities of the internship program are clearly defined and understood. The internship offers the students an opportunity to gain hands-on industrial or organizational exposure; to integrate the knowledge and skills acquired through the coursework; interact with professionals and other interns; and to improve their presentation, writing, and communication skills. Internship offen acts as a gateway for final placement for many students.

A student shall opt for carrying out the Internship at an Industry/Research Organization or at another institute of higher learning and repute (Academia). The organization for Internship shall be selected/decided by the students on their own with prior approval from the faculty advisor/respective PG Programme Coordinator/Guide/Supervisor. Every student shall be assigned an internship Supervisor/Guide at the beginning of the Internship. The training shall be related to their specialization after the second semester for a minimum duration of six to eightweeks. On completion of the course, the student is expected to be able to develop skills in facing and solving the problems experiencing in the related field.

#### **Objectives**

- Exposure to the industrial environment, which cannot be simulated in the classroom and hence creating competent professionals for the industry.

- Provide possible opportunities to learn understand and sharpen the real timetechnical / managerial skills required at the job.

- Exposure to the current technological developments relevant to the subjectarea of training.

- Create conducive conditions with quest for knowledge and its applicabilityon the job.

- Understand the social, environmental, economic and administrative considerations that influence the working environment.

• Expose students to the engineer's responsibilities and ethics.

# **Benefits of Internship**

#### **Benefits to Students**

- An opportunity to get hired by the Industry/ organization.

- Practical experience in an organizational setting & Industry environment.

- Excellent opportunity to see how the theoretical aspects learned in classes are integrated into the practical world. On-floor experience provides much more professional experience which is often worth more than classroom teaching.

- Helps them decide if the industry and the profession is the best career optionto pursue.

- Opportunity to learn new skills and supplement knowledge.

- Opportunity to practice communication and teamwork skills.

- Opportunity to learn strategies like time management, multi-tasking etc in an industrial setup.

- Makes a valuable addition to their resume.

- Enhances their candidacy for higher education/placement.

- Creating network and social circle and developing relationships with industry people.

- Provides opportunity to evaluate the organization before committing to afull time position.

# **Benefits to the Institute**

- Build industry academia relations.

- Makes the placement process easier.

- Improve institutional credibility & branding.

- Helps in retention of the students.

- Curriculum revision can be made based on feedback from Industry/students.

- Improvement in teaching learning process.

# **Benefits to the Industry**

- Availability of ready to contribute candidates for employment.

- Year round source of highly motivated pre-professionals.

- Students bring new perspectives to problem solving.

- Visibility of the organization is increased on campus.

- Quality candidate's availability for temporary or seasonal positions and projects.

- Freedom for industrial staff to pursue more creative projects.

- Availability of flexible, cost-effective workforce not requiring a longtermemployer commitment.

- Proven, cost-effective way to recruit and evaluate potential employees.

- Enhancement of employer's image in the community by contributing to the educational enterprise.

## **Types of Internships**

- Industry Internship with/without Stipend

- Govt / PSU Internship (BARC/Railway/ISRO etc)

- Internship with prominent education/research Institutes

- Internship with Incubation centres /Start-ups

#### Guidelines

- All the students need to go for internship for minimum duration of 6 to 8 weeks.

- Students can take mini projects, assignments, case studies by discussing it with concerned authority from industry and can work on it during internship.

- All students should compulsorily follow the rules and regulations as laid by industry.

- Every student should take prior permissions from concerned industrial authority if they want to use any drawings, photographs or any other document from industry.

- Student should follow all ethical practices and SOP of industry.

- Students have to take necessary health and safety precautions as laid by the industry.

- Student should contact his /her Guide/Supervisor from college on weeklybasis to communicate the progress.

- Each student has to maintain a diary/log book

- After completion of internship, students are required to submit

- Report of work done

- Internship certificate copy

- Feedback from employer / internship mentor

- Stipend proof (in case of paid internship).

**Total Marks 100:** The marks awarded for the Internship will be on the basis of (i)Evaluation done by the Industry (ii) Students diary (iii) Internship Report and (iv) Comprehensive Viva Voce.

# **Continuous Internal Evaluation: 50 marks**

| Student's diary                 | - 25 Marks |

|---------------------------------|------------|

| Evaluation done by the Industry | - 25 Marks |

**Student's Diary/ Daily Log**: The main purpose of writing daily diary is to cultivate the habit of documenting and to encourage the students to search for details. It develops the students' thought process and reasoning abilities. The students shouldrecord in the daily training diary the day to day account of the observations, impressions, information gathered and suggestions given, if any. It should contain the sketches & drawings related to the observations made by the students. The dailytraining diary should be signed after every day by the supervisor/ in charge of the section where the student has been working. The diary should also be shown to the Faculty Mentor visiting the industry from time to time and got ratified on the day ofhis visit. Student's diary will be evaluated on the basis of the following criteria:

- Regularity in maintenance of the diary

- Adequacy & quality of information recorded

- Drawings, design, sketches and data recorded

- Thought processand recording techniques used

- Organization of the information.

# The format of student's diary

Name of the Organization/Section:

Name and Address of the Section Head:

Name and Address of the Supervisor:

Name and address of the student:

Brief description about the nature of internship:

| Buy sketches, result observed, issues identified, data recorded, etc. | Day | Brief write up about the Activities carried out: Such as design, sketches, result observed, issues identified, data recorded, etc. |

|-----------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------|

| 1 |  |

|---|--|

|   |  |

| 2 |  |

|   |  |

| 3 |  |

|   |  |

Signature of Industry Supervisor

Signature of Section Head/HR

Manager

Office Seal

# **Attendance Sheet**

Name of the Organization/Section:

Name and Address of the Section Head:

Name and Address of the Supervisor:

Name and address of the student:

# Internship Duration: From ...... To

.....

| Month & Year    | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 |  |

|-----------------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|--|

|                 |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |  |

| Month<br>& Year |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |  |

|                 |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |  |

| Month & Year    |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |  |

|                 |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |  |

Signature of Industry Supervisor

Signature of Section Head/HR

Manager

Office Seal

Note:

• Student's Diary shall be submitted by the students along with attendance record and an evaluation sheet duly signed and stamped by the industry to the Institute immediately after the completion of the training.

- Attendance Sheet should remain affixed in daily training diary. Do notremove or tear it off.

- Student shall sign in the attendance column. Do not mark 'P'.

- Holidays should be marked in red ink in the attendance column. Absentshould be marked as 'A' in red ink.

## **Evaluation done by the Industry (Marks 25)**

# Format for Supervisor Evaluation of Intern

Student Name : \_\_\_\_\_ Date: \_\_\_ Dupervisor Name : \_\_\_\_\_ Designation: \_\_\_\_

Company/Organization :\_\_\_\_\_

Internship Address: \_\_\_\_\_ Dates of Internship: From\_\_\_To

# Please evaluate intern by indicating the frequency with which you

observed following parameters:

| Parameters Marks                       | Needs<br>improvement<br>(0 – 0.25<br>mark) | Satisfactory<br>(0.25–0.50<br>mark) | Good<br>(0.75<br>mark) | Excellent<br>(1 mark) |

|----------------------------------------|--------------------------------------------|-------------------------------------|------------------------|-----------------------|

| Behavior                               |                                            |                                     |                        |                       |

| Performs in a dependable Manner        |                                            |                                     |                        |                       |

| Cooperates with coworkers and          |                                            |                                     |                        |                       |

| supervisor                             |                                            |                                     |                        |                       |

| Shows interest in work                 |                                            |                                     |                        |                       |

| Learns quickly                         |                                            |                                     |                        |                       |

| Shows initiative                       |                                            |                                     |                        |                       |

| Produces high quality work             |                                            |                                     |                        |                       |

| Accepts responsibility                 |                                            |                                     |                        |                       |

| Accepts criticism                      |                                            |                                     |                        |                       |

| Demonstrates organizational skills     |                                            |                                     |                        |                       |

| Uses technical knowledge and expertise |                                            |                                     |                        |                       |

| Shows good judgment                    |                                            |                                     |                        |                       |

| Demonstrates creativity/originality    |                                            |                                     |                        |                       |

| Analyzes problems effectively          |                                            |                                     |                        |                       |

| Is self-reliant                        |                                            |                                     |                        |                       |

| Communicates well                      |                                            |                                     |                        |                       |

| Writes effectively                     |                                            |                                     |                        |                       |

Mar Athanasius College of Engineering (Govt. Aided & Autonomous) M Tech Regulations, Curriculum 2024

| Has a professional attitude     |  |  |

|---------------------------------|--|--|

| Gives a professional appearance |  |  |

| Is punctual                     |  |  |

| Uses time effectively           |  |  |

Overall performance of student

Intern (Tick one) : Needs improvement (0 - 0.50 mark) / Satisfactory (0.50 – 1.0 mark) / Good (1.5 mark) / Excellent (2.0 mark)Additional comments, if any (2 marks) :

Signature of Industry Supervisor Signature of Section Head/HRManager

Office Seal

# End Semester Evaluation (External Evaluation): 50 Marks

| Internship Report | - | 25 Marks |

|-------------------|---|----------|

| Viva Voce         | - | 25 Marks |

**Internship Report**: After completion of the internship, the student should prepare a comprehensive report to indicate what he has observed and learnt in the training period and should be submitted to the faculty Supervisor. The student may contact Industrial Supervisor/ Faculty Mentor for assigning special topics and problems and should prepare the final report on the assigned topics. Daily diary willalso help to a great extent in writing the industrial report since much of the information has already been incorporated by the student into the daily diary. The training report should be signed by the Internship Supervisor, Programme Coordinator and Faculty Mentor.

The Internship report (25 Marks) will be evaluated on the basis of following criteria:

- Originality

- Adequacy and purposeful write-up

- o Organization, format, drawings, sketches, style, language etc.

- Variety and relevance of learning experience

- Practical applications, relationships with basic theory and concepts taughtin the

Viva Voce (25 Marks) will be done by a committee comprising Faculty Supervisor, PG Programme Coordinator and an external expert (from Industry or research/academic Institute). This committee will be evaluating the internship reportalso.

# (v) LABORATORY COURSES

Lab work and Viva-voce : 60 marks

Final evaluation Test and Viva voce : 40 marks

The laboratory courses will be having only Continuous Internal Evaluation and carries 100 marks. Final evaluation shall be done by two examiners; one examiner willbe a senior faculty from the same department.

## (vi) INDUSTRY INTEGRATED COURSE

Engineering students frequently aspire to work in areas and domains that are key topics in the industry. There are concerns by recruiters that skill sets of engineering students did not match with the Industry requirements, especially in the field of latest topics. In response to their desires, the College has incorporated Industry integrated course in the curriculum.

The evaluation pattern for Industry based electives is as follows:

#### **Continuous Internal Evaluation: 40 marks**

| End Semester Examination                  | : 60 marks |

|-------------------------------------------|------------|

| Test paper 2 (Module 3 and Module 4)      | : 10 marks |

| Test paper 1 (Module 1 and Module 2)      | : 10 marks |

| interpretation/Case study                 | : 10marks  |

| Course based task/Seminar/Data collection | and        |

| Seminar                                   | : 10 marks |

The examination will be conducted by the College with the question paper provided by the Industry. The examination will be for 3 Hrs and will contain 7 questions, with minimum one question from each module of which student should answer any five. Each question can carry 12 marks. The valuation of the answer scripts shall be done by the expert in the Industry handling the course.

#### (vii) MOOC COURSES

The MOOC course shall be considered only if it is conducted by the agencies namely AICTE/NPTEL/SWAYAM or NITTTR. The MOOC course should have a minimum duration of 8 weeks and the content of the syllabus shall be enough for at least 40 hours of teaching. The course should have a proctored/offline end semester examination. The students can do the MOOC according to their convenience, but shall complete it before the end of fourth semester. The list of MOOC courses will be provided by the concerned BoS if at least 70% of the course content match with the area/stream of study. The course shall not be considered if its content has more than 50% of overlap with a core/elective course in the concerned discipline or with an open elective.

MOOC Course to be successfully completed before the end of fourth semester (starting from semester 1). A credit of 2 will be awarded to all students whoever successfully completes the MOOC course as per the evaluation pattern of the respective agency conducting the MOOC.

#### (viii) MINIPROJECT

#### Total marks: 100, only CIE

Mini project can help to strengthen the understanding of student's fundamentals through application of theoretical concepts and to boost their skills and widen the horizon of their thinking. The ultimate aim of an engineering student is to resolve a problem by applying theoretical knowledge. Doing more projects increases problem-solving skills. The introduction of mini projects ensures preparedness of students to undertake dissertation. Students should identify a topic of interest in consultation with PG Programme Coordinator. Demonstrate the novelty of the project through the results and outputs. The progress of the mini project is evaluated based on three reviews, two interim reviews and a final review. A report is required at the end of the semester.

Interim evaluation: 40 (20 marks for each review), final evaluation by a Committee (will be evaluating the level of completion and demonstration of functionality/specifications, clarity of presentation, oral examination, work knowledge and involvement): 35, Report (the committee will be evaluating for the technical content, adequacy of references, templates followed and permitted plagiarism level is not more than 25%): 15, Supervisor/Guide: 10

#### (ix) **DISSERTATION**

**Dissertation:** All Students should carry out the dissertation in the college or can work either in any CSIR/Industrial R&D organization/any other reputed Institute which have facilities for dissertation work in the area proposed.

**Dissertation outside the Institute**: For doing dissertation outside the Institution, the following conditions are to be met:

- They have completed successfully the course work prescribed in the approved curriculum up to the second semester.

- They should choose Track 2 in semester 3 and 4

- The student has to get prior approval from the DLAC and CLAC.

- Facilities required for doing the dissertation shall be available in the Organization/Industry (A certificate stating the facilities available in the proposed organization and the time period for which the facilities shall be made available to the student, issued by a competent authority from the Organization/Industry shall be submitted by the student along with the application).

- They should have an external as well as an internal supervisor. The internal supervisor should belong to the parent institution and the external supervisor should be Scientists or Engineers from the Institution/Industry/ R&D organization with which the student is associated for doing the dissertation work. The external supervisor shall be with a minimum post graduate degree in the related area.

- The student has to furnish his /her monthly progress as well as attendance report

signed by the external guide and submit the same to the concerned Internal guide.

• The external guide is to be preferably present during all the stages of evaluation of the dissertation.

Note1- Students availing this facility should continue as regular students of the College itself.

Note 2-The course work in the 3rd semester is to be completed as per the curriculum requirements (i) MOOC can be completed as per the norms mentioned earlier

**Internship leading to Dissertation:** The M. Tech students who after completion of 6 to 8 weeks internship at some reputed organization are allowed to continue their work as dissertation for the third and fourth semester after getting approval from theDLAC. Such students shall make a brief presentation regarding the work they propose to carry out before the DLAC for a detailed scrutiny and to resolve its suitability for accepting it as an M.Tech dissertation. These students will be continuing as regular students of the Institute in third semester for carrying out all academic requirements as per the curriculum/regulation. However, they will be permitted to complete their dissertation in the Industry/Organization (where they have successfully completed their internship) during fourth semester.

**Dissertation as part of Employment:** Students may be permitted to discontinue the programme and take up a job provided they have completed all the courses till second semester (FE status students are not permitted) prescribed in the approved curriculum. The dissertation work can be done during a later period either in the organization where they work if it has R & D facility, or in the Institute. Such students should submit application with details (copy of employment offer, plan of completion of their project etc.) to the Dean (PG) through HoD. The application shallbe vetted by CLAC before granting the approval. When the students are planning todo the dissertation work in the organization with R & D facility where they are employed, they shall submit a separate application having following details:

- Name of R&D Organization/Industry

- Name and designation of an external supervisor from the proposed Organization/Industry (Scientists or Engineers with a minimum post graduate degree in the related area) and his/her profile with consent

- Name and designation of a faculty member of the Institute as internal supervisor with his/her consent

- Letter from the competent authority from the Organization/Industry granting permission to do the dissertation

- Details of the proposed work

- Work plan of completion of project

DLAC will scrutinize the proposal and forward to CLAC for approval.

When students are doing dissertation work along with the job in the organization (with R & D facility) where they are employed, the dissertation work shall be completed in four semesters normally (two semesters of dissertation work along with the job may be considered as equivalent to one semester of dissertation work at the Institute). Extensions may be granted based on requests from the student and recommendation of the supervisors such that he/she will complete the M. Tech programme within four years from the date of admission as per the regulation. Method of evaluation and grading of the dissertation will be the same as in the case of regular students. The course work in the 3rd semester for such students are to be completed as per the curriculum requirements (i) MOOC can be completed as per the norms mentioned earlier. However, for self learning students, all evaluations shall be carried out in their parent Institution as in the case of regular students.

# **Mark Distribution:**

Phase 1: Total marks: 100, only CIE

# Phase 2: Total marks: 200, CIE = 100 and ESE = 100 marks

- Maximum grade (S grade) for the dissertation phase II will be awarded preferably if the student publishes the dissertation work in a peer reviewed journal.

- Final Evaluation (ESE) should be done by a three-member committee comprising of the Department Project coordinator, Guide and an External expert. The external expert shall be an academician or from industry.

# (x) TEACHING ASSISTANCESHIP (TA)

All M.Tech students irrespective of their category of admission, shall undertakeTA duties for a minimum duration as per the curriculum. Being a TA, the student will get an excellent opportunity to improve their expertise in the technical content of the course, enhance communication skills, obtain a hands-on experience in handling the experiments in the laboratory and improve peer interactions. The possible TA responsibilities include the following: facilitate a discussion section or tutorial for a theory/ course, facilitate to assist the students for a laboratory course, serve as a mentor for students, and act as the course webmaster. TAs may berequired to attend the instructor's lecture regularly. A TA shall not be employed as a substitute instructor, where the effect is to relieve the instructor of his or her teaching responsibilities.

#### For the tutorial session:

- (i) Meet the teacher and understand your responsibilities well in advance, attend the lectures of the course for which you are a tutor, work out the solutions for all the tutorial problems yourself, approach the teacher if you find any discrepancy or if you need help in solving the tutorial problems, use reference text books, be innovative and express everything in English only.

- (ii) Try to lead the students to the correct solutions by providing appropriate hints rather than solving the entire problem yourself, encourage questions from the students, lead the group to a discussion based on their questions, plan to ask them some questions be friendly and open with the students, simultaneously being firm with them.

- (iii) Keep track of the progress of each student in your group, give a periodic feedback to the student about his/her progress, issue warnings if the student is consistently under-performing, report to the faculty if you find that a particular student is consistently underperforming, pay special attention to slow-learners and be open to the feedback and comments from the students and faculty.

- (iv) After the tutorial session you may be required to grade the tutorials/assignments/tests. Make sure that you work out the solutions to the questions yourself, and compare it with the answer key, think and work out possible alternate solutions to the same question, understand the marking scheme from the teacher. Consult the teacher and make sure that you are not partial to some student/students while grading. Follow basic ethics.

#### Handling a laboratory Session:

- (i) Meet the faculty in- charge a few days in advance of the actual lab class and get the details of the experiment, get clarifications from him/her regarding all aspects of the experiment and the expectations, prepare by reading about the theoretical background of the experiment, know the physical concepts involved in the experiment, go to the laboratory and check out the condition of the equipment/instrumentation, perform the laboratory experiment at least once one or two days before the actual laboratory class, familiarize with safety/ security aspects of the experiment / equipment/laboratory, prepare an instruction sheet for the experiment in consultation with the faculty, and keep sufficient copies ready for distribution to students for their reference.

- (ii) Verify condition of the equipment/set up about 30 minutes before the students arrive in the class and be ready with the hand outs, make brief introductory remarks about the experiment, its importance, its relevance to the theory they have studied in the class, ask the students suitable questions to know there level of preparation for the experiment, discuss how to interpret results, ask them comment on the results.

- (iii) Correct/evaluate/grade the submitted reports after receiving suitable instructions from the faculty in charge, continue to interact with students if they have any clarifications regarding any aspect of the laboratory session, including of course grading, Carefully observe instrument and human safety in laboratory class, Preparing simple questions for short oral quizzing during explanation of experiments enables active participation of students, facilitate attention, provides feedback and formative evaluation.

# POINTS TO REMEMBER

- 1. Arrange an awareness programme to all M.Tech students on day 1 regarding the curriculum and the regulation.

- 2. The departments should prepare the list of MOOC courses suitable to their programmes and encourage the students to complete at the earliest.

- 3. Make a tie up with industries by the middle of semester for Industry Integrated

Course. While choosing the course, it should be ensured that the programme is relevant and updated in that discipline. The Industry expert handling the course shall be a postgraduate degree holder. The evaluation procedure shall also be clearly explained to them.

- 4. Each department offering M.Tech programme should be careful in selectingthe mini project in semester 2.

- 5. The departments should invite the Industries/research organizations during first semester and inform them about the mandatory 6-8 weeks internship that the students should undergo after their second semester. The possibility of doing their dissertation at the Industry shall also be explored. They should also be made aware about the evaluation procedure of the Internships. They may also be informed that it is possible to continue internship provided if it leads to their dissertation. Proposals may be collected from them for allotting to students according to their fields of interest.

- 6. Make sure that all internal evaluations and the end semester examinations to be conducted by the college are carried out as per the evaluation procedure listed in the curriculum. Any dilution from the prescribed procedure shall be viewed seriously.

- 7. Teaching assistance shall be assigned to all students as per the curriculum. However, a TA shall not be employed as a substitute instructor, where the effect is to relieve the instructor of his or her teaching responsibilities.

- 8. The possible TA responsibilities include the following: facilitate a discussion section or tutorial for a theory/ course, facilitate to assist the students for a laboratory course, serve as a mentor for students, and act as the course web-master.

\*\*\*\*\*\*

# **SEMESTER 1**

# **Discipline: ELECTRONICS AND COMMUNICATION**

# Stream: VLSI AND EMBEDDED SYSTEMS

Mar Athanasius College of Engineering (Govt. Aided & Autonomous), Kothamangalam

| CODE       | COURSE NAME              | CATEGORY | L | Т | Р | S | CREDIT |

|------------|--------------------------|----------|---|---|---|---|--------|

| M24EC1T101 | Digital CMOS VLSI Design | Core     | 4 | 0 | 0 | 4 | 4      |

**Preamble:** This course aims to develop students a good knowledge of all aspects of Digital CMOS VLSI Design, its characteristics, designing and model various subsystems using CMOS logic.

Prerequisite: Solid State Devices, Basic MOS Transistor Theory

**Course Outcomes:** After the completion of the course the student will be able to

| CO 1        | Design basic CMOS digital circuits and model the circuits to     |

|-------------|------------------------------------------------------------------|

|             | analyze the delay                                                |

| <b>CO 2</b> | Understand interconnect, power analyses, I/O and clocking issues |

|             | of CMOS Digital circuits                                         |

| CO 3        | Design various types of static and dynamic digital CMOS circuits |

| CO 4        | Understand the timing concepts in latch and flip-flops.          |

| CO 5        | Design CMOS data path subsystems and memory arrays               |

## Mapping of course outcomes with program outcomes

|             | <b>PO 1</b> | PO 2 | PO 3 | PO 4 | PO 5 | PO 6 |

|-------------|-------------|------|------|------|------|------|

| CO 1 🌙      | 2           | 2    | 3    | 3    | 2    | 2    |

| CO 2        | 2           | 2    | 3    | 3    | 2    | 2    |

| CO 3        | 2           | 2    | 2    | 3    | 2    | 2    |

| <b>CO 4</b> | 2           | 2    | 3    | 3    | 2    | 2    |

| CO 5        | 2           | 2    | 3    | 3    | 2    | 2    |

#### **Assessment Pattern**

|            | Digital CMOS VL          | $\sim$       |                          |  |  |

|------------|--------------------------|--------------|--------------------------|--|--|

| Bloom's    |                          | ous Internal | End Semester Examination |  |  |

| Category   | Test 1                   | Test 2       | (% Marks)                |  |  |

| 1          | (% Mark <mark>s</mark> ) | (%Marks)     |                          |  |  |

| Remember   | XX                       | XX           | XX                       |  |  |

| Understand | 20                       | 20           | 20                       |  |  |

| Apply      | 40                       | 40           | 40                       |  |  |

| Analyse    | 30                       | 30           | 30                       |  |  |

| Evaluate   | 10                       | 10           | 10                       |  |  |

| Create     | XX                       | XX           | XX                       |  |  |

#### Mark distribution

| Total | CIE   | ESE   | ESE      |

|-------|-------|-------|----------|

| Marks | marks | marks | Duration |

| 100   | 40    | 60    | 3 Hours  |

# M Tech in VLSI and Embedded Systems Continuous Internal Evaluation Pattern:

| Micro project/Course based project   | :10 marks |

|--------------------------------------|-----------|

| Course based task/Seminar/Quiz       | :10 marks |

| Test paper 1 (Module 1 and Module 2) | :10 marks |

| Test paper 2 (Module 3 and Module 4) | :10 marks |

**End Semester Examination Pattern:** The end semester examination will be conducted by the college. There will be two parts; Part A and Part B. Part A contain 5 numerical questions (such questions shall be useful in the testing of knowledge, skills, comprehension, application, analysis, synthesis, evaluation and understanding of the students), with 1 question from each module, having 4 marks for each question. Students shall answer all questions. Part B contains 7 questions (such questions shall be useful in the testing of overall achievement and maturity of the students in a course, through long answer questions relating to theoretical/practical knowledge, derivations, problem solving and quantitative evaluation), with minimum one question from each module of which student shall answer any five. Each question can carry 8 marks. Total duration of the examination will be 3 Hrs.

# SY<mark>LLA</mark>BUS

# MODULE 1 (9 hours)

# Introduction to CMOS technology:

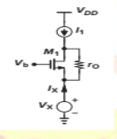

MOS Transistor Theory: IV and CV characteristics.

**CMOS logic**: NOT, NAND, NOR, Compound Logic, Pass transistor, Transmission gate, Tristate logic, Multiplexer.

**Basics of CMOS fabrication and Layout**: Fabrication Process, Layout Design Rules, Stick Diagrams, Design partitioning, Logic design, Circuit design, Physical design, Design verification, Fabrication, Packaging and testing.

Static CMOS Inverter: DC Characteristics, Beta Ratio Effects, Noise Margin, Pass Transistor DC Characteristics.

# **MODULE 2 (9 hours)**

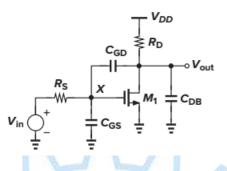

Delay Models: Introduction, Definitions, Timing Optimization.

**RC Delay Model**: Effective Resistance, Gate and Diffusion Capacitance, Equivalent RC Circuits, Elmore Delay, Layout Dependence of Capacitance, Determining Effective Resistance.

Linear Delay Model: Logical Effort, Parasitic Delay, Delay in a Logic Gate.

Logical Effort of Paths: Delay in Multistage Logic Networks, Choosing the Best Number of Stages.

# MODULE 3 (9 hours)

**Interconnect effects and power analysis**: Introduction, Wire Geometry and Interconnect Modelling: Resistance, Capacitance, and Inductance.

Interconnect Impact: Delay, Energy, Crosstalk, Inductive Effects, Effective Resistance and Elmore Delay.

Power: Sources of Power Dissipation, Dynamic Power, Static Power, On-Chip Power Distribution

Mar Athanasius College of Engineering (Govt. Aided & Autonomous), Kothamangalam

# M Tech in VLSI and Embedded Systems

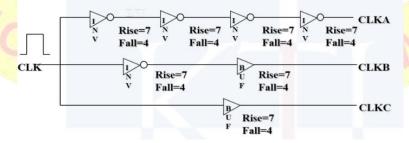

Network. On-Chip Bypass Capacitance, Power Network Modelling, Power Supply Filtering, Charge Pumps. Energy Scavenging. **Clocks:** Clock System Architecture, Global Clock Generation, Global Clock Distribution, Local Clock Gaters. PLLs and DLLs. **I/O**: Basic I/O Pad Circuits, Electrostatic Discharge Protection.

# MODULE 4 (9 hours)

# **Combinational Circuit Design**

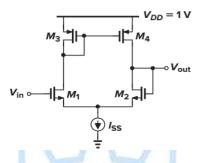

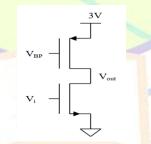

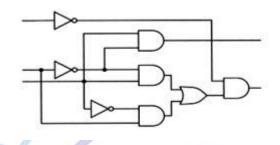

**Static CMOS circuits:** Ratioed Circuits, CMOS Inverter, tristate inverter, Other static CMOS logic gates, static properties (2 input NAND, NOR), Combinational logic circuits.

**Fundamentals of dynamic logic**: Dynamic pass transistor circuits, CMOS circuits, High performance dynamic circuits-Domino CMOS, Multi Output Domino Logic, NP Domino logic (NORA),

BiCMOS: NOT, NAND and NOR

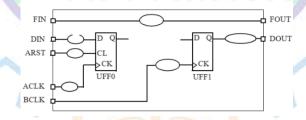

FF and Latches: True-Single-Phase-Clock (TSPC) CMOS logic.

Silicon-On-Insulator Circuit Design: Floating Body Voltage, SOI Advantages, Disadvantages. Introduction to System on chip (SOC).

Introduction to System on chip (SOC).

# MODULE 5 (9 hours)

# Data path Subsystems:

Adders: Single-Bit Addition, Carry-Propagate Addition, Subtraction, Multiple-Input Addition Multipliers: Unsigned Array Multiplication, Booth Encoding, Column Addition, Final Addition. Shifters: Funnel Shifter, Barrel Shifter.

Comparators: Magnitude Comparator.

Counters: Binary Counters.

**Designing of memory and array structures:** SRAM, DRAM, and Embedded DRAM. Read-Only Memory, Content-Addressable Memory, Programmable Logic Arrays.

# **Reference Books**

- 1. Weste and Harris, CMOS VLSI Design A Circuits and Systems Perspective, 4/E, Pearson

- 2. Weste and Harris, "Integrated Circuit Design", 4/e, 2011, Pearson Education.

- 3. Sung-Mo Kang, Yusuf Leblebici, "CMOS Digital Integrated Circuits, 3/e, Tata McGraw-Hill Education, 2003.

- 4. Rabaey, Chandrakasan and Nikolic, "Digital Integrated Circuits A Design Perspective", 2/e, Pearson Education.

- 5. R. Jacob Baker, Harry W. Li, David E. Boyce, "CMOS, Circuit Design, Layout, and Simulation", 3/e, Wiley Interscience.

# M Tech in VLSI and Embedded Systems COURSE CONTENTS AND LECTURE SCHEDULE

| No         | Торіс                                                                                                    | No. of Lecture/          |

|------------|----------------------------------------------------------------------------------------------------------|--------------------------|

|            |                                                                                                          | Tutorial hours           |

|            | Module 1                                                                                                 | -                        |

| 1.1        | MOS Transistor Theory: IV and CV characteristics.                                                        | 1                        |

| 1.2        | CMOS logic: NOT, NAND, NOR, Compound Logic, Pass                                                         | 2                        |

|            | transistor, Transmission gate, Tristate logic, Multiplexer.                                              |                          |

| 1.3        | Basics of CMOS fabrication and Layout: Fabrication                                                       | 3                        |

|            | Process, Layout Design Rules, Stick Diagrams, Design                                                     |                          |

|            | partitioning, Logic design, Circuit design, Physical design,                                             |                          |

|            | Design verification, Fabrication, Packaging and testing.                                                 |                          |

| 1.4        | Static CMOS Inverter: DC Characteristics, Beta Ratio                                                     | 2                        |

|            | Effects, Noise Margin.                                                                                   |                          |

| 1.5        | Pass Transistor DC Characteristics                                                                       | 1                        |

|            | Module 2                                                                                                 |                          |

| 2.1        | <b>Delay Models</b> : Introduction, Definitions, Timing                                                  | 1                        |

| the second | Optimization.                                                                                            |                          |

| 2.2        | RC Delay Model: Effective Resistance, Gate and                                                           | 3                        |

| 1          | Diffusion Capacitance, Equivalent RC Circuits, Elmore                                                    | Name of Street, or other |

|            | Delay, Layout Dependence of Capacitance, Determining                                                     |                          |

|            | Effective Resistance.                                                                                    |                          |

| 2.3        | Linear Delay Model: Logical Effort, Parasitic Delay,                                                     | 3                        |

|            | Delay in a Logic Gate.                                                                                   |                          |

| 2.4 🍡      | Logical Effort of Paths: Delay in Multistage Logic                                                       | 2                        |

|            | Networks, Choosing the Best Number of Stages.                                                            |                          |

| 2.1        | Module 3                                                                                                 |                          |

| 3.1        | Interconnect effects and power analysis: Introduction,                                                   | 2                        |

|            | Wire Geometry and Interconnect Modelling: Resistance,                                                    |                          |

| 2.0        | Capacitance, and Inductance.                                                                             | 2                        |

| 3.2        | Interconnect Impact: Delay, Energy, Crosstalk, Inductive                                                 | 2                        |

| 22         | Effects, Effective Resistance and Elmore Delay.                                                          | 2                        |

| 3.3        | <b>Power:</b> Sources of Power Dissipation, Dynamic Power,                                               | 2                        |

| 1 11-      | Static Power, On-Chip Power Distribution Network. On-<br>Chip Pupess Capacitance Power Network Modelling |                          |

| A          | Chip Bypass Capacitance, Power Network Modelling,<br>Power Supply Filtering, Charge Pumps. Energy        | 200                      |

|            | Scavenging.                                                                                              | S                        |

| -          | Seavenging.                                                                                              |                          |

| 3.4        | Clocks: Clock System Architecture, Global Clock                                                          | 2                        |

| J. T       | Generation, Global Clock Distribution, Local Clock Gaters.                                               |                          |

|            | PLLs and DLLs.                                                                                           |                          |

|            |                                                                                                          |                          |

| 3.5        | I/O: Basic I/O Pad Circuits, Electrostatic Discharge                                                     | 1                        |

|            | Protection.                                                                                              |                          |

|            |                                                                                                          |                          |

|            | Module 4                                                                                                 | 1                        |

| 4.1        | Static CMOS circuits: Ratioed Circuits, CMOS Inverter,                                                   | 3                        |

|            | tristate inverter, Other static CMOS logic gates, static                                                 |                          |

| 1          | properties (2 input NAND, NOR), Combinational logic                                                      | 1                        |

|     | r Embedded Systems                                     |                                                                                                                |

|-----|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|     | circuits.                                              |                                                                                                                |

| 4.2 | Fundamentals of dynamic logic: Dynamic pass transistor | 2                                                                                                              |

|     | circuits, CMOS circuits, High performance dynamic      |                                                                                                                |

|     | circuits-Domino CMOS, Multi Output Domino Logic, NP    |                                                                                                                |

|     | Domino logic (NORA)                                    |                                                                                                                |

| 4.3 | <b>BiCMOS</b> : NOT, NAND and NOR                      | 1                                                                                                              |

| 4.4 | FF and Latches: True-Single-Phase-Clock (TSPC) CMOS    | 1                                                                                                              |

|     | logic 🦳 🦳 👝                                            |                                                                                                                |

| 4.5 | Silicon-On-Insulator Circuit Design: Floating Body     | 1                                                                                                              |

|     | Voltage, SOI Advantages, Disadvantages                 |                                                                                                                |

| 4.6 | Introduction to System on chip (SOC).                  | 1                                                                                                              |

|     | Introduction to Network on chip (NOC).                 |                                                                                                                |

|     | Module 5                                               |                                                                                                                |

| 5.1 | Adders: Single-Bit Addition, Carry-Propagate Addition, | 2                                                                                                              |

|     | Subtraction, Multiple-Input Addition                   |                                                                                                                |

| 5.2 | Multipliers: Unsigned Array Multiplication, Booth      | 2                                                                                                              |

| 10  | Encoding, Column Addition, Final Addition.             | And and a second se |

|     |                                                        |                                                                                                                |

| 5.3 | Shifters: Funnel Shifter, Barrel Shifter.              | 1                                                                                                              |

|     |                                                        |                                                                                                                |

| 5.4 | Comparators: Magnitude Comparator.                     | 1                                                                                                              |

| 5.5 | Counters: Binary Counters                              | 1                                                                                                              |

| 5.6 | <b>Designing of memory and array structures:</b> SRAM, | 2                                                                                                              |

| 0   | DRAM, and Embedded DRAM. Read-Only Memory,             |                                                                                                                |

|     | Content-Addressable Memory, Programmable Logic         |                                                                                                                |

|     | Arrays                                                 |                                                                                                                |

VOWLED

# **Model Question Paper**

**QP CODE**:

Reg No.:\_\_\_\_\_

Name:

# MAR ATHANASIUS COLLEGE OF ENGINEERING (AUTONOMOUS), KOTHAMANGALAM

# FIRST SEMESTER M.TECH DEGREE EXAMINATION, DECEMBER 2024

# Course Code: M24EC1T101

Course Name: Digital CMOS VLSI Design

Max. Marks:60

Duration: 3 hours

Pages: 2

# PART A

# Answer all questions. Each question carries 4 marks.

1. Suppose VDD = 3.2 V and Vt = 0.4 V. Determine Vout for the following circuit. Neglect the body effect.

V<sub>DD</sub> ⊥ V<sub>in</sub> ⊥ V<sub>out</sub>

> Vin = 0 V Vin = 0.6 V Vin = 0.9 VVin = 3.2 V.

- 2. Model an nMOS transistor with width equal to 2. Draw the equivalent circuit.

- 3. What is electrostatic discharge protection? Draw the circuit for the same.

- 4. Describe the tristate CMOS inverter.

- 5. Illustrate how a subtraction can be implemented using adder.

# PART B

# Answer any five questions. Each question carries 8 marks.

6. a. Design a static CMOS inverter with equal rise and fall resistance. What is the effect of beta ratio in the working of inverter? (4 marks)

b. Draw the cross-sectional view of the fabrication procedure involved in a CMOS inverter. Draw the stick encoding of the CMOS inverter. (4 marks)

7. a. Sketch a transistor-level schematic for a CMOS 4-input NOR gate. Find out the width of transistors to achieve unit rise and fall resistance. (4 marks)

b. Design an unit inverter driving 4 identical unit inverter. Draw the RC model and find out the propagation delay. R=10K and C=0.1Pf. (4 marks)

a. A unit inverter is driving 4 unit inverter at the end of a 1mm long, 0.32μm wide wire in a 180nm Mar Athanasius College of Engineering (Govt. Aided &Autonomous), Kothamangalam M Tech in VLSI and Embedded Systems

process. The sheet resistance is 0.050hms/square and the capacitance is 0.2 fF/ $\mu$ m. Find the Elmore delay by constructing a  $\pi$  model for the wire. Resistance of unit nMOS is 10K $\Omega$  and gate capacitance is 0.1pF. (4 marks)

b How crosstalk affects the data transmission in an interconnect wire. What are the different methods of cross- talk control? (4 marks)

9. a. Design a dynamic CMOS inverter cascaded with another dynamic inverter. Draw the timing diagram and explain the monotonicity problem. How we can eliminate this problem. (4 marks)

b. Design a 3-input BiCMOS NAND gate. Label the transistor widths. What is the logical effort? (4 marks)

10. a. With proper timing diagram explain the working of NP Domino logic. (4 marks)

b. Sketch a transistor level schematic of the following functions:

(i) Y=(A+B).C+D.E

(ii) Y=(A+B).(C+D) (4 marks)

11. a. With proper schematics explain the how a PG carry ripple adder is implemented. (4 marks)

b. Sketch and explain the working principle of a 4 bit barrel shifter. (4 marks)

12. a. Design a carry skip adder and explain. (4 marks)

b. Explain with example a RADIX 4 booth encoding multiplier. (4 marks)

| CODE       | COURSE NAME       | CATEGORY | L | Т | Р | S | CREDIT |

|------------|-------------------|----------|---|---|---|---|--------|

| M24EC1T102 | FPGA BASED SYSTEM | Core     | 4 | 0 | 0 | 4 | 4      |

|            | DESIGN            |          |   |   |   |   |        |

**Preamble:** The purpose of this course is to introduce basic concepts of FPGA based system design and to impart practical skills in developing a synthesizable digital sub system using Verilog HDL.

# **Course Outcomes:** After the completion of the course the student will be able to

| CO 1 | Apply Verilog programming to develop and simulate digital sub systems. (Cognitive Knowledge Level: Apply) |

|------|-----------------------------------------------------------------------------------------------------------|

| CO 2 | Design RT-level combinational and regular sequential circuits (Cognitive                                  |

|      | Knowledge Level: Create)                                                                                  |

| CO 3 | Construct FSM and FSMD (Cognitive Knowledge Level: Analyse)                                               |

| CO 4 | Analyse and implement UART subsystems in FPGA (Cognitive Knowledge Level:<br>Evaluate)                    |

| CO 5 | Explain architecture and features of programmable logic devices (Cognitive Knowledge Level: Analyse)      |

# Mapping of course outcomes with program outcomes

|      | PO 1 | PO 2 | PO 3 | PO 4 | PO 5 | PO 6 |

|------|------|------|------|------|------|------|

| CO 1 | 2    |      | 3    | 2    | 2    | 1    |

| CO 2 | 3    |      | 3    | 3    | 2    | 1    |

| CO 3 | 1    |      | 2    | 3    | 2    | 1    |

| CO 4 |      |      | 2    | 3    | 2    | 1    |

| CO 5 | 2    |      | 3    | 3    | 3    | 1    |

# **Assessment Pattern**

| · / / O             | FPGA BASED          | SYSTEM DESIGN            |                                      |

|---------------------|---------------------|--------------------------|--------------------------------------|

| Bloom's<br>Category |                     | ous Internal<br>aluation | End SemesterExamination<br>(% Marks) |

|                     | Test 1<br>(% Marks) | Test 2<br>(%Marks)       | SPU                                  |

| Remember            | XX                  | XX                       | XX                                   |

| Understand          | 20                  | 20                       | 20                                   |

| Apply               | 40                  | 40                       | 40                                   |